UP009N10LT TOLT 패키지-산업용 어플리케이션을 위해 설계된 MOSFETs

산업용 애플리케이션에서 MOSFETs에 대한 수요가 증가하고 있다.기계적 솔루션부터 더욱 까다로운 응용 조건에 이르기까지 반도체 제조업체는 새로운 패키징 솔루션을 개발하고 기술적 개선을 구현해야 합니다.TO-252와 같은 오리지널 서피스 마운트 디바이스 (SMDS)부터 최신 핀 프리 패키지 및 내부 실리콘 기술의 상당한 개선에 이르기까지 MOSFET 솔루션은 산업 시장의 새로운 요구 사항을 더 잘 충족하도록 진화하고 있다.여기에서는 UOE의 TOLT 패키지, 열 성능 및 보드 신뢰성을 다룹니다.

주요 기능, 주요 이점 및 애플리케이션:

주요 특징:

* 초저 RDS (on)

* 300A 이상의 높은 정격 전류

* 탑 열 방산

* 네거티브 핀 본체 높이 차이

* Wuxi 냉각 패드

주요 장점:

* 높은 시스템 효율성, 연장된 배터리 수명

고전력 밀도 (High power density)

* 우수한 열 성능, 열 방출 시스템을 절약

* 히트 싱크에 대한 열 저항을 최소화합니다

중요 한 응용 프로그램:

모바일 로봇 (Mobile robot)

* 드 론

경전기자동차 (Light electric vehicle)

전기 적재 트럭 (Electric loading truck)

전기자전거 (Electric bicycle)

전동공구 (Power tools)

배터리 관리 시스템 (Battery management system)

Target application 시장

UOE의 톨 패키지 파워 MOSFETs은 매우 높은 전력 레벨을 달성하는 데 도움을 줍니다.탑 쿨링을 통한 열 저항 향상 덕분에 TOLT는 장치 수와 시스템 크기를 늘리지 않고도 전력을 요구하는 애플리케이션의 요구를 충족할 수 있습니다.따라서 TOLT 패키지의 핵심 애플리케이션은 고전류 애플리케이션이다.이 패키지는 최대 50 kW의 전력 레벨을 가진 고전력 모터 드라이버에 적합합니다.

패키지 디자인

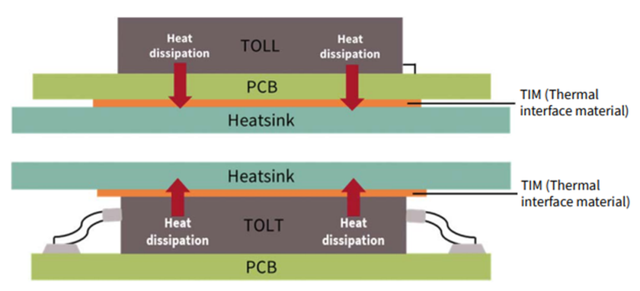

새로운 톨트 패키지의 컨셉은 일반적인 바닥 쿨링 파워 MOSFETs 와는 다르다.TOLT 에서는 패키지의 리드 프레임이 반전되고 드레인 패드 (칩 하단 = 드레인 연결부) 가 패키지 상단에 노출됩니다.

그림 1 톨트의 측면 모습

그림 2 패키지 모습

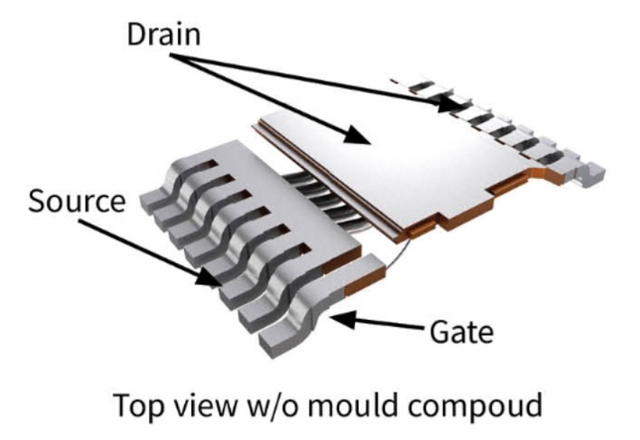

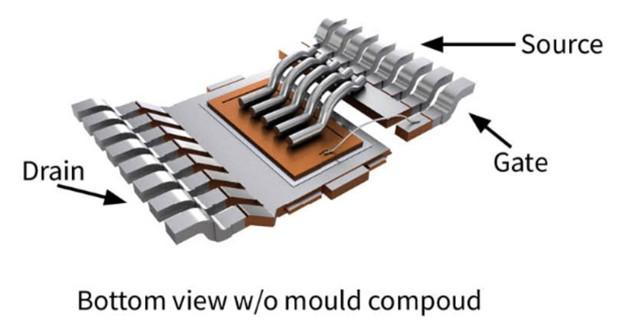

그림 3과 4는 그리드, 소스 및 배수 핀을 보여줍니다.보드와의 배수 연결을 위해 상단의 맨 패드에 8개의 핀이 한 줄로 연결되어 있습니다.패키지 반대편에는 1개의 핀이 게이트 제어에 사용되고 나머지 7개의 핀은 전류 소스에 연결됩니다.

그림 3 TOLT 3D view

그림 4 톨트 하단 전경

TOLT 장점 및 원칙

1, 상단 열 소산은 더 높은 응용 력을 얻을 수있을뿐만 아니라 여러 다른 중요한 이점도 얻을 수 있습니다.표준 방열 방식 (그림 6)에서 히트 싱크는 일반적으로 PCB 아래에 설치됩니다.칩에서 외부로의 열 전달 경로는 다음과 같습니다:이 솔루션의 단점은 PCB 및 TIM/thermal paste 파라미터에 따라 열 성능이 저하됩니다.이러한 부품의 열전도도가 나쁘면 과열 및 응용 전력이 저하될 수 있으며, 높은 방열 비용을 의미하기도 합니다.또한 조립 보드는 더 높은 온도를 견뎌야 하므로 더 비싼 PCBS를 사용해야 합니다.

그림 5 후방 방열 모드에서의 열 경로

2.SMD 컴포넌트를 PCB (그림 10) 하단의 톨트 MOSFET 아래에 배치하여 가용 영역을 최적화할 수 있습니다.

그림 6 톨 & 톨트 방열량 개략도

3. TOLT는 전류/전력 처리 용량을 증가시킵니다.TOLT package에 비해 RthJA는 20% 절감되고, RthJC는 50% 가까이 개선되며, Rth(J-heatsink)는 36% 절감된다.

4. 여분의 이용

냉각 시스템의 더 높은 전력 밀도 또는 비용 절감 달성 외에도 TOLT 제품은 다른 장점을 가지고 있습니다.다음은 몇 가지 예입니다:

히트 싱크가 PCB 아래에 설치되지 않고 MOSFET의 아래쪽을 통해 보드로 열이 전달되지 않기 때문에 게이트 드라이버나 커패시터를 PCB의 반대쪽에 배치할 수 있습니다.이러한 솔루션은 PCB 공간을 더욱 효율적으로 사용할 수 있습니다.

증가 creepage 거리 (근원과 배출 전위 사이의 거리).

유리전이온도가 낮은 PCBS를 사용할 수 있습니다.

적은 열이 PCB 및 주변 부품으로 전달됩니다.

5. Thermal interface 재료 두께

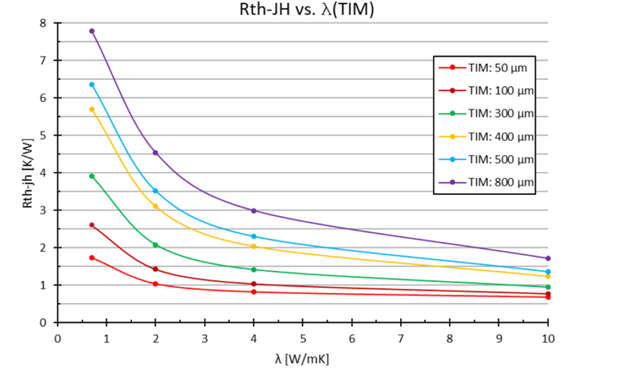

TOLT 패키지의 최상의 열 성능을 보장하고 패키지의 열 저항을 최대한 낮게 보장하기 위해서는 TIM 두께를 최적화하는 것이 필수적입니다.아래는 접합에서 핀까지 총 RTH에 미치는 영향을 분석하기 위해 TOLT 패키지에 대한 여러 다른 TIM 두께의 시뮬레이션이며, 시뮬레이션에서는 히트싱크 온도가 주변 온도 85°C로 고정됩니다.

그림 7은 TIM 두께에 따른 TIM 열전도율과 Rth의 상관관계를 보여준다

그림에서 볼 수 있듯이, TIM이 얇을수록 열 저항은 낮아집니다.지불 해야 하지만, 관심을 열전도 율 (λ) 값의 팀.더 나은 열전도도는 TIM 두께의 부정적인 영향을 보상합니다.

시판되는 기존 TIMs의 열전도도는 일반적으로 3~6 W/mK 사이입니다.최적의 열 성능과 적절한 전기적 격리 위상 균형을 달성하기 위해 시스템 엔지니어는 TIM의 두께와 열 파라미터를 최적화해야 합니다.

고객이 가장 일반적으로 사용하고 시장에서 널리 사용되는 소재는 3~4 W/mK 범위의 열전도도를 가진 TIM입니다.이 값의 시뮬레이션에 따르면 MOSFET 접합 부분과 히트싱크 사이의 열 저항은 TIM 두께에 따라 0.8~3K/W 사이로 변화한다.실제 팀을 때 두께는 300~500 μ m, 그 열 저항 2.4K/W. 5에 도달 할 수 있다.Rth 가 2.4 K/W와 같고 MOSFET 접속과 하우징 사이의 온도차가 90°C 일 때 (Tcase = 85°C, Tjmax = 175°C로 가정), 단일 톨트 MOSFET은 약 40 W의 전력을 소비할 수 있다.

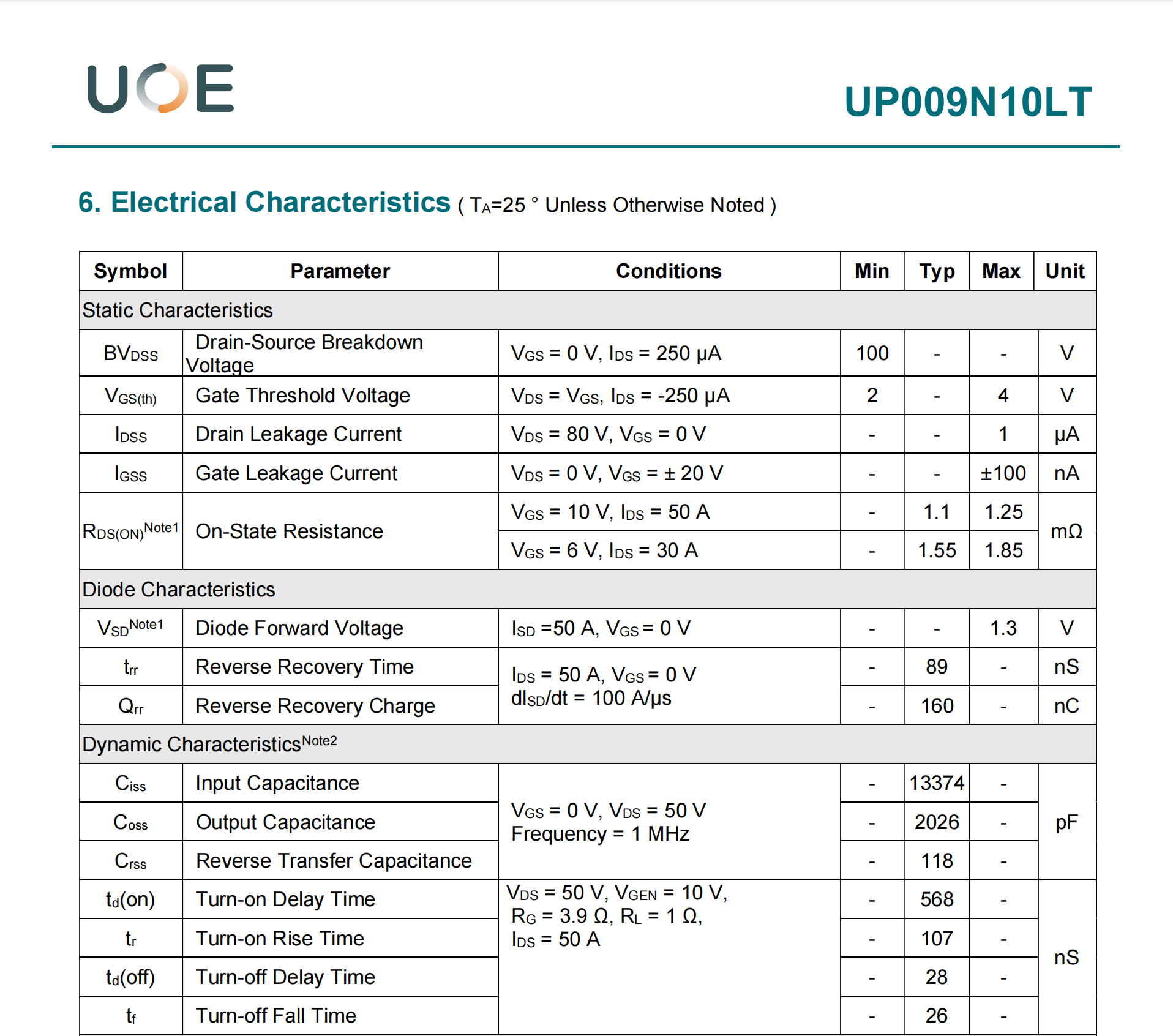

6. 전기 매개 변수

TOLT 패키지의 MOSFETs는 해당 톨 부품과 동일한 RDS(on) 값을 갖는다.예를들어, 훌륭 한 100V MOSFETs에서 TOLT 패키지 (UP009N10LT) 및 그에 상응하는 톨 (UP009N10T), RDS (에), 맥스는 모두 1. 25 m Ω이다.

TOLL에 비해 관통홀과 주위온도가 85°C인 일반 2s2p 보드에서 TOLT를 가장 크게 개선한 것은 히트싱크와의 접합에 대한 열저항 Rth를 크게 감소시킨 것입니다.Rth 가 50% 가까이 감소하므로 총 소멸전력이 90% 이상 증가한다.

요약

새로운 탑쿨링 톨트 패키지는 고출력 산업용 애플리케이션을 위해 FR4 PCBS에 구현된다.TOLT는 코어 접합부에서 히트 싱크로 가는 열 경로를 단축시켜 열 저항을 향상시킴으로써 전기적 성능을 향상시킵니다.